- 您现在的位置:买卖IC网 > Sheet目录3873 > PIC18F45K20-I/MV (Microchip Technology)MCU 32KB FLASH 1536B RAM 40-UQFN

2007

Micr

ochip

T

e

ch

nol

ogy

I

n

c.

P

reli

m

inary

DS

70165E

-page

49

dsPIC33F

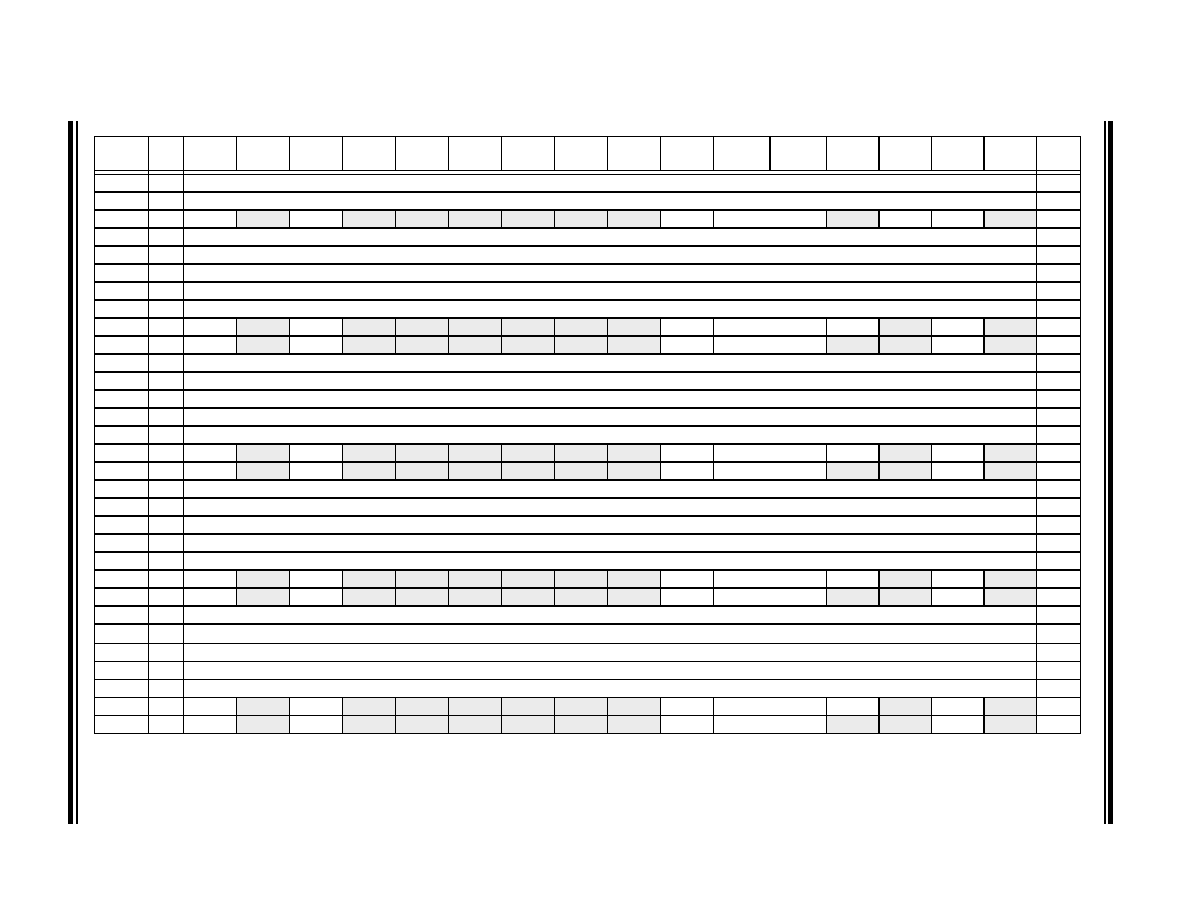

TABLE 3-4:

TIMER REGISTER MAP

SFR

Name

SFR

Addr

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 9

Bit 8

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

All

Resets

TMR1

0100

Timer1 Register

xxxx

PR1

0102

Period Register 1

FFFF

T1CON

0104

TON

—

TSIDL

—

TGATE

TCKPS<1:0>

—

TSYNC

TCS

—

0000

TMR2

0106

Timer2 Register

xxxx

TMR3HLD

0108

Timer3 Holding Register (for 32-bit timer operations only)

xxxx

TMR3

010A

Timer3 Register

xxxx

PR2

010C

Period Register 2

FFFF

PR3

010E

Period Register 3

FFFF

T2CON

0110

TON

—

TSIDL

—

TGATE

TCKPS<1:0>

T32

—

TCS

—

0000

T3CON

0112

TON

—

TSIDL

—

TGATE

TCKPS<1:0>

—

TCS

—

0000

TMR4

0114

Timer4 Register

xxxx

TMR5HLD

0116

Timer5 Holding Register (for 32-bit operations only)

xxxx

TMR5

0118

Timer5 Register

xxxx

PR4

011A

Period Register 4

FFFF

PR5

011C

Period Register 5

FFFF

T4CON

011E

TON

—

TSIDL

—

TGATE

TCKPS<1:0>

T32

—

TCS

—

0000

T5CON

0120

TON

—

TSIDL

—

TGATE

TCKPS<1:0>

—

TCS

—

0000

TMR6

0122

Timer6 Register

xxxx

TMR7HLD

0124

Timer7 Holding Register (for 32-bit operations only)

xxxx

TMR7

0126

Timer7 Register

xxxx

PR6

0128

Period Register 6

FFFF

PR7

012A

Period Register 7

FFFF

T6CON

012C

TON

—TSIDL

—

TGATE

TCKPS<1:0>

T32

—TCS

—

0000

T7CON

012E

TON

—TSIDL

—

TGATE

TCKPS<1:0>

—

—TCS

—

0000

TMR8

0130

Timer8 Register

xxxx

TMR9HLD

0132

Timer9 Holding Register (for 32-bit operations only)

xxxx

TMR9

0134

Timer9 Register

xxxx

PR8

0136

Period Register 8

FFFF

PR9

0138

Period Register 9

FFFF

T8CON

013A

TON

—

TSIDL

—

TGATE

TCKPS<1:0>

T32

—

TCS

—

0000

T9CON

013C

TON

—

TSIDL

—

TGATE

TCKPS<1:0>

—

TCS

—

0000

Legend:

x

= unknown value on Reset, — = unimplemented, read as ‘0’. Reset values are shown in hexadecimal.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16CR76T-I/SS

IC PIC MCU 8KX14 28SSOP

PIC18F13K50-I/P

IC PIC MCU FLASH 4KX16 20-PDIP

PIC16CR76T-I/SO

IC PIC MCU 8KX14 28SOIC

PIC18LF24K22-I/MV

IC PIC MCU 16KB FLASH 28UQFN

PIC18LF24K22-I/ML

IC PIC MCU 16KB FLASH 28QFN

PIC16CR76T-I/ML

IC PIC MCU 8KX14 28QFN

PIC16F627-04/P

IC MCU FLASH 1KX14 COMP 18DIP

PIC18F45J10-I/ML

IC PIC MCU FLASH 16KX16 44QFN

相关代理商/技术参数

PIC18F45K20-I/P

功能描述:8位微控制器 -MCU 32KB Flash 1536B RAM 25 I/O 8B RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45K20-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 1536B RAM 25 I/O 8B RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45K20T-I/ML

功能描述:8位微控制器 -MCU 32KB Flash 1536B RAM 25 I/O 8B RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45K20T-I/MLV01

制造商:Microchip Technology Inc 功能描述:

PIC18F45K20T-I/MV

功能描述:8位微控制器 -MCU 32KB FL 1536b RAM 8b Familynanowatt XLP

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45K20T-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 1536B RAM 25 I/O 8B RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45K22-E/ML

功能描述:8位微控制器 -MCU 32KB Flash 1536B RAM 8B nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45K22-E/MV

功能描述:8位微控制器 -MCU 32KB 1536b RAM 8bit familynanoWatt XLP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT